# 素子フィルタを対象とした パラメトリック最適化の基礎検討

Basic study of parametric optimization for element filters

陳和平<sup>1)</sup> 野村勝也<sup>2)</sup> 山崎慎太郎<sup>3)</sup>

Chen Heping, Katsuya Nomura and Shintaro Yamasaki

<sup>1)</sup>早稲田大学大学院 情報生産システム研究科 (〒808-0135 福岡県北九州市若松区ひびきの2-7,

E-mail: chenheping@fuji.waseda.jp)

<sup>2)</sup>博士(工学) 関西学院大学 工学部 専任講師 (〒669-1330 兵庫県三田市学園上ヶ原1番,

E-mail: katsuya.nomura@kwansei.ac.jp)

<sup>3)</sup>博士(工学) 早稲田大学大学院 情報生産システム研究科 教授 (〒808-0135 福岡県北九州市若松区ひびきの2-7,

E-mail: s\_yamasaki@waseda.jp)

Element filters with capacitor elements and inductor elements are used as a type of noise filter to eliminate electromagnetic noise. In an elemental filter, the conductor layout connecting the elements has a significant impact on the noise rejection performance. Our research aims to improve noise reduction performance by parametric optimization of the conductor layout of element filters.

**Key Words :** EMI design, Parameter optimization, Noise filter

## 1. はじめに

電気自動車（以下、EV 省略）の発展に伴い、欠かせない半導体技術も進化している。EV は電子機器で構成されているため、半導体の性能が EV の性能に直結する。その中で、新型 EV の開発に伴い、電圧変換を担う電源システムの開発も不可欠だ。EV の高電圧リチウムイオンバッテリーからの出力は高圧であり、DC/DC コンバータによって他の電力部品が使用される 12V 電圧に変換される。しかし、DC/DC コンバータの半導体スイッチは多く、スイッチの ON/OFF を切り替えるに伴って発生する電子ノイズが電磁干渉を引き起こす。ノイズを「車載受信機保護のための妨害波の限度値及び測定法」規格 CISPR 25 の限度値以下に抑えるため、ノイズフィルター回路が DC/DC コンバータ中に用いている [1]。

ノイズフィルター回路の設計は複数な要因に影響されている。事例に応じて支配的な要因も変わるので、高性能な汎用可能設計法はない。一例として、電子部品の寄生インダクタンスや磁気結合なども半導体に影響があるので、理想的な数学モデルが抽出は難しい [2]。伝統的な手法では、数年の設計経験を持つ技術者が様々な対策を試し、有効なものを見つける。そのため、コンピュータ支援設計だけでなく、実際の実験も行われますが、これには非常に時間がかかる [3,4]。

近年、多くの研究がノイズフィルター回路の設計支援方法を提案している。例えば、野村らは、トポロジー最適化を用いて高性能なノイズフィルターの材料分布を生成した [5]。最適化できたノイズフィルターは高性能するけど、形状は不規則なので生産は難しい。本論文では、パラメータ最適化手法を用いて、実際の製造に適した高性能ノイズフィルター回路設計支援方法を論

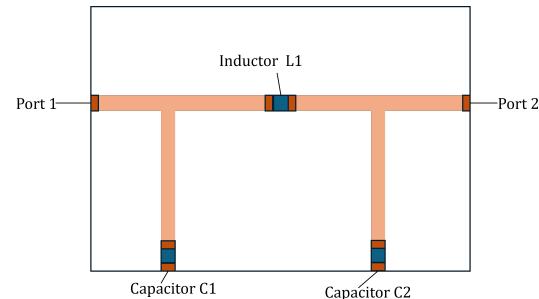

図-1 ノイズフィルターの構造図

じる。

本論文の構成は以下の通りである。まず、パラメータ最適化に基づくノイズフィルター設計方法が提案される。そして DC/DC コンバータ中のノイズフィルタ最適化を行い、回路設計支援方法の有効性を検証する。また、最適化結果から、今後より良い設計案を得るために方向を示している。

## 2. 実験方法

### (1) パラメーター最適化の概念

本研究使われているパラメーター最適化法は、ノイズフィルタの導体形状生成問題から、導体材料ノード座標と導体の幅までに変換する。その中、ノイズフィルタ中各素子の間に導体材料に繋ぐ、導体形状ができた。

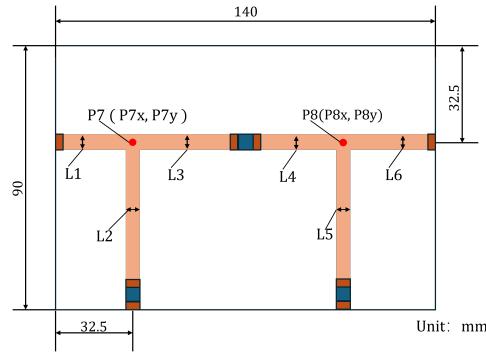

ここでは、図 2 に示すように、設計変数は導体材料ノードの座標 P7 と P8、各導体の幅 L1~L6 だ。P7 と P8 は、直線で 3 つの素子に接続される。左側の電源入力ポート（図 1 の Port 1 部分）から P7 までの直線の幅

図-2 設計変数の設定

を L1 に設定し、P7 から下部素子への接続の幅を L2、P7 から中間素子への接続の幅を L3 とする。P8 から中間素子への接続の幅を L4 に設定し、P8 から下部素子までの直線の幅を L5、P8 から出力ポート（図 1 の Port 2 部分）までの直線の幅を L6 とする。

$$P_7(P_{7x}, P_{7y}) \quad P_{7x} \in (10e - 3, 60e - 3) \quad (1)$$

$$P_{7y} \in (12e - 3, 90e - 3)$$

$$P_8(P_{8x}, P_{8y}) \quad P_{8x} \in (80e - 3, 133e - 3) \quad (2)$$

$$P_{8y} \in (12e - 3, 90e - 3)$$

$$L_{i,i \in N(1,6)} \in (1.1e - 3, 3e - 3) \quad (3)$$

$$f(x), \quad y = \{P_{7x}, P_{7y}, P_{8x}, P_{8y}, L_1, L_2, L_3, L_4, L_5, L_6\} \quad (4)$$

$$\nabla = \frac{f(x + \Delta) - f(x)}{\Delta} \quad (5)$$

(1) 式から (5) 式まで、ここで  $P_7(P_{7x}, P_{7y})$  と  $P_8(P_{8x}, P_{8y})$  は導体接続点の座標。 $L_{i,i \in N(1,6)}$  は導体の幅。 $f(x)$  は有限要素分析モデル計算できた  $S_{21}$  の値。 $\nabla$  は設計変数に微小な変化  $\Delta$  を追加し計算した 1 次勾配。

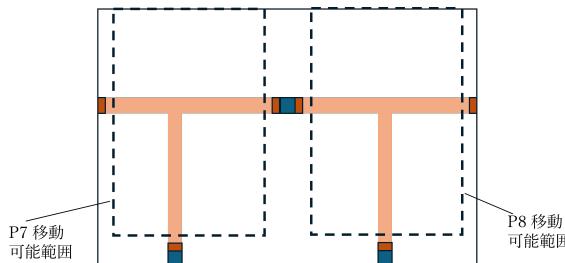

生成された材料が素子お互いに短絡を防止するため、導体ノード P7 と P8 の設計範囲を縮小した。同時に、断線を回避するため L1～L6 の上限と下限を設定した。下限の選択基準は、生成された直線導体が断線しないことを保証する。上限の選択基準は、導体が領域を超えて広すぎと、素子の間に短絡にならない。

## (2) 最急降下法

本研究では文献 [6] で紹介された最急降下法を採用し、COMSOL を用いてデバイスのシミュレーションを行う。これにより、設計変数の勾配を求め、その勾配に基づいて設計変数の変化方向を決定した。

勾配を計算するため適切な方法が必要だ。通常、勾配法と非勾配法によって最適化をする [6]。勾配法は、設計変数の勾配を求めることができる場合に使用され、

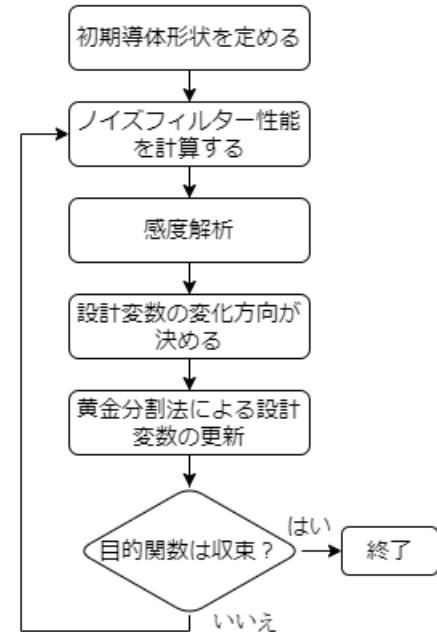

図-3 最急降下法のフロー

異なる方向での微小な変化に対する目的関数の変化量を計算した。一方、非勾配法（遺伝的アルゴリズムを含む）は、計算時間が膨大になるため、この問題には適していない [7]。本文では勾配法を採用している。

各設計変数をパラメータ最適化するため、最適化のフローチャートを図 3 示す。まず、初期導体形状を定める、COMSOL で初期導体形状のノイズフィルターの性能を計算する。次に、設計変数に微小な変化を加え、ノイズフィルター性能の感度解析を行い、設計変数と目的関数の勾配を得られる。勾配に基づいて設計変数の変化する方向が決めた。そして、変化する方向が得られたら、その方向で最も優れた点を判断するために黄金分割法を使用し、更新された設計変数が得られた。収束まで最適化反復を繰り返す、最適化された導体形状を導出する。

$$x^{(k+1)} = x^{(k)} + \nabla^{(k)} * d^{(k)} \quad (6)$$

(6) 式で、 $x^{(k)}$  は最適化探索中の設計変数。 $\nabla^{(k)}$  は設計変数がここでの勾配。 $d^{(k)}$  は優れた探索距離。

update  $d^{(k)}$  :

if  $g(d_{\text{left center}}) > g(d_{\text{right center}})$

$$d_{\min}^{(k)} = d_{\min}^{(k)}$$

$$d_{\max}^{(k)} = d_{\max}^{(k)} - \rho^{(k)} \cdot d_{\max}^{(k)} \quad (7)$$

else:

$$d_{\min}^{(k)} = d_{\min}^{(k)} + \rho^{(k)} \cdot d_{\max}^{(k)}$$

$$d_{\max}^{(k)} = d_{\max}^{(k)}$$

(7) 式は  $d^{(k)}$  が黄金分割探索法で更新している判断条件だ。ここで、 $d_{\max}^{(k)}$  は、座標 P7 と P8 が設計変数と

図-4 設計区域の設定

して使用される場合、図4の設計領域内で最適な変化する方向で最も優れた点を判断する際の最大距離だ。計算を短縮するため、ここは $\rho^{(k)}=0.25$ として、黄金分割探索回数条件は設計変数の座標P7、P8が5回、設計変数の導体幅L1～L6が30回を設定した。

### 3. 実験

#### (1) A: 設計目標

図1に目標フィルタの回路図と構造が示されている。先行研究[8]で述べられているフィルタと同様に、設計された部品はノイズフィルターだ。

ノイズフィルタを使用して、パラメータの最適化プロセスがノイズフィルターの性能改善を検証する。回路はπ形状のノイズフィルタを採用し、πの各ポートにはインダクタ一個とキャパシタ二個が接続されている。回路基板の幅は50mm、奥行きは22mm、厚みは1.6mm、比誘電率は4.5だ。

この問題の設計領域は、図2に示すように、電子部品の上面図を選択した。導体形状の分布を最適化し、ここでP7とP8は平面内の座標を表し、L1からL6は導体の幅だ。信号の入力ポートから各素子へ、そして各素子から出力ポートへ接続される領域を設計領域を設定する。導体の誤った接続を防ぐために、各素子が接続不可な所を制定した。

#### (2) B: 最適化設定

ノイズフィルタの役割は、CISPR22の規定された周波数帯域内の伝導ノイズを減少するので、目的関数は周波数f、高周波帯域10MHzと0.1MHzを設定する。最適化目標がこの二つ周波数で $S_{21}$ のdB値を最小化する。

パラメータの最適化には、一次法の最急降下法、共役勾配法、二次法のニュートン法方法がある[6]。本研究では、設計変数の二次導関数を得ることができないため、一次法を採用する。原因としては、設計変数が微小な変化を加えて、設計変数の勾配が得るの計算法として、二次導関数を計算する場合、必要な計算回数が膨大になり計算できなくなる。同時に、断線や短絡が発生しないため、設計変数の各導体接続ノード座標(P7とP8)と導体の幅(L1～L6)に対し制約条件が設定された。

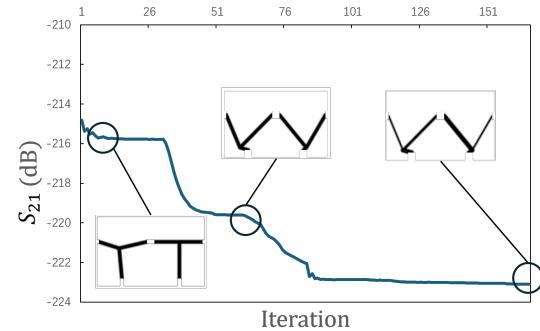

図-5 最適化履歴

### 4. 結果

図4には、最適化の履歴が示す。目標周波数10MHzと0.1MHzの $S_{21}$ を加えて、7.726dB低下し、ノイズフィルター効果が3.59%上がった。計算時間は、20時間だ。

この設計手法は、より複雑な設計問題に応用も可能だ。将来の研究では、設計自由度を増加する。例えば、設計変数中導体接続ノード座標の数を増加し、直線が折れ線に変わり、さらに優れた性能を期待している。その上、製品を軽量化するため、設計されたノイズフィルター基板のサイズを減少する、そこで最適化を行う。

### 5. 結論

本研究では、パラメータ最適化に基づくノイズフィルター設計手法を提案した。パラメータ最適化は有限要素モデルによって電磁場をシミュレートし、ノイズ低減するための勾配を導出した。勾配の値に基づいてパラメータの変化を決定し、パラメータ決定された導体構造を繰り返し更新することで、高性能な構造設計を導出した。また、パラメータ最適化の履歴から、設計改善の指針を得ることができ、同時に断線や短絡を防止するための制約関数を作成し、最適化終了条件を決めた。

### 参考文献

- [1] M. Caponet et al., "EMI filters design for power electronics", Proc. IEEE 33rd Annu. Power Electron. Spec. Conf. 2002, vol. 4, pp. 2027-2032.

- [2] A. Zhou et al., "Study and modeling of intercomponent coupling to optimize EMC filter", Proc. 10th Int. Symp. Electromagn. Compat, pp. 518-522, 2011.

- [3] S. Wang et al., "Investigation of hybrid EMI filters for common-mode EMI suppression in a motor drive system", IEEE Trans. Power Electron., vol. 25, no. 4, pp. 1034-1045, Oct. 2009.

- [4] Y. Maillet et al., "High-density EMI filter design for DC-fed motor drives", IEEE Trans. Power Electron., vol. 25, no. 5, pp. 1163-1172, Dec. 2009.

- [5] Takahashi A, Nomura K, Kojima T, et al. Fabrication and evaluation of a magnetically coupled EMI filter designed with topology optimization[J]. IEEE Transactions on Power Electronics, 2021, 36(11): 12620-12630.

- [6] Kochenderfer M J, Wheeler T A. Algorithms for optimization[M]. Mit Press, pp. 69–74, 2019.

- [7] O. Sigmund, “On the usefulness of non-gradient approaches in topology optimization,” Structural and Multidisciplinary Optimization, vol. 43, no. 5, pp. 589–596, 2011

- [8] Nomura K. Density-based Topology Optimization for Conductor Design of EMI filters with Improved Impedance Boundary Condition[C]//2022 International Symposium on Electromagnetic Compatibility–EMC Europe. IEEE, 2022: 377-382.

- [9] T, ” Parallel computing of 3-D eddy-current analysis with  $\$A\text{-}\phi\$$  method for rotating machines ”, IEEE Trans. Magn., vol. 48, no. 2, pp. 975-978, Feb. 2012.